# Lecture Notes in Computer Science

4147

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Manfred Broy Ingolf H. Krüger Michael Meisinger (Eds.)

# Automotive Software – Connected Services in Mobile Networks

First Automotive Software Workshop, ASWSD 2004 San Diego, CA, USA, January 10-12, 2004 Revised Selected Papers

#### Volume Editors

Manfred Broy Institut für Informatik Technische Universität München Boltzmannstr. 3 D-85748 Garching, Germany E-mail: broy@informatik.tu-muenchen.de

Ingolf H. Krüger University of California, San Diego Computer Science and Engineering 9500 Gilman Drive La Jolla, CA 92093-0404, USA E-mail: ikrueger@cs.ucsd.edu

Michael Meisinger Institut für Informatik Technische Universität München Boltzmannstr. 3 D-85748 Garching, Germany E-mail: meisinge@informatik.tu-muenchen.de

Library of Congress Control Number: 2006932846

CR Subject Classification (1998): C.2.4, C.3, C.4, C.5.3, D.1.3, D.2.1, D.2.2, D.2.3, D.2.4, D.2.7, D.2.11, D.2.12, D.2.13, D.3.1, D.4, H.3-5, J.7

LNCS Sublibrary: SL 3 – Information Systems and Application, incl. Internet/Web and HCI

ISSN 0302-9743

ISBN-10 3-540-37677-1 Springer Berlin Heidelberg New York ISBN-13 978-3-540-37677-4 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2006 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11823063 06/3142 5 4 3 2 1 0

## Preface

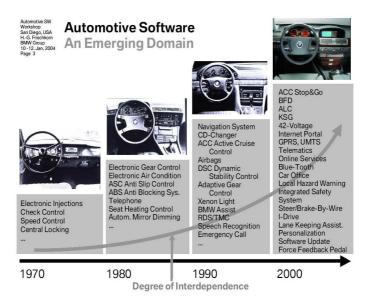

Software development for the automotive domain is currently subject to a silent revolution. On the one hand, software has become the enabling technology for almost all safety-critical and comfort functions offered to the customer. A total of 90 % of all innovations in automotive systems are directly or indirectly enabled by software. Today's luxury cars contain up to 80 electronic control units (ECUs) and 5 different, inter-connected network platforms, over which some 700 software-enabled functions are distributed.

On the other hand, the complexity induced by this large number of functions, their interactions, and their supporting infrastructure has started to become *the* limiting factor for automotive software development. Adequate management of this complexity is particularly important; the following list highlights three of the corresponding challenges:

First, the dependencies between safety-critical and comfort functions are rapidly increasing; a simple example is the interplay of airbag control and power seat control in the case of an accident. Careful analysis and design of these dependencies are necessary to yield correct software solutions.

Second, advances in wired and wireless networking infrastructures enable interconnection between cars and backend service providers (e.g., to call for help in cases of emergency), between cars and devices brought into the car by drivers and passengers (such as cell phones, PDAs, and laptops), and even among cars. This dramatically shifts the focus from the development of individual software solutions residing on dedicated ECUs to their distribution and interaction within and beyond car boundaries.

Third, the myriad of functions and services offered to the driver and passengers need to be effectively accessible without compromising traffic safety. This requires user interfaces addressing not only ease of use but also priority of information necessary for safe vehicle operation, and choice of interface modality (e.g., voice versus pushing of buttons for menu selection) for reasons of adequacy or user limitations.

These challenges are aggravated by demanding time-to-market requirements, short development cycles, rapid change of technological infrastructures, customer demands, and product lines. The silent revolution currently underway in the automotive domain thus consists of a shift of focus from hardware to software infrastructures and from ECUs to software services as the center of concern in the development process. This puts the *software architecture* for future generation automotive systems in the spotlight as a critical element both for enabling advanced services supporting drivers and passengers, and for managing the complexity of these functions amidst the high safety demands they are subject to.

The goal for the first Automotive Software Workshop, San Diego, ASWSD 2004, was to bring together experts from industry and academia, who work on highly

complex, distributed, reactive software systems related to the automotive domain, and to discuss and further the understanding of the following focus areas:

- Automotive Software and Software Architectures

- Automotive Domain Architectures

- Automotive Software Services

- Automotive Hardware, Middleware, and Software Platforms

- On- and Off-Board Ad-Hoc Networking

- Networked Automotive Services

- Mobile Sensor Networks

- Reliability, Security and Privacy for Automotive Software

- Enabling Technologies for Telematics Applications

The workshop, which took place during January 10–12, 2004 in La Jolla, CA, USA, contributed to fostering a deeper understanding of the research challenges and agendas in this area. Potentials for cross-disciplinary research, as well as pertinent curricula and training programs to address these challenges were identified and discussed.

The workshop program consisted of 4 keynote presentations, 22 technical paper presentations and 2 panel discussions. The workshop spanned two-and-a-half days and was divided into the following topical sessions: Quality Assurance (QA), Networking Infrastructures and Applications (NI), Real-Time Control (RT), Services and Components (SC), and Model-Based Development and Tools (MD). The pre-proceedings, consisting of the presentation slide sets, were made available at <a href="http://aswsd.ucsd.edu/2004">http://aswsd.ucsd.edu/2004</a>.

To foster discussion on cross-cutting and interdisciplinary topics the organizers decided to have four keynote presentations (two from industry and two from academia) and two panel discussions as integral parts of the workshop program. Hans-Georg Frischkorn (then BMW Group), Hermann Kopetz (TU Vienna), K. Venkatesh Prasad (Ford Motor Company), and Janos Sztipanovits (Vanderbilt University) were recruited as keynote speakers. Professor Larry Smarr (Director, Calit2) delivered opening remarks on the first day of the workshop.

Hans-Georg Frischkorn (then Senior Vice President System Architecture and System Integration, BMW Group) delivered the opening keynote "Automotive Software – The Silent Revolution" in the Quality Assurance session, where he laid out BMW's automotive software vision to realize innovative software-based functionality in cars. He stressed the importance of software architectures and infrastructures, and promoted an open software platform providing extensibility, updatability and support for easy integration of new functionality. Frischkorn showed how the tasks of operating and maintaining future vehicle generations could be supported by system services provided on multiple layers of abstraction.

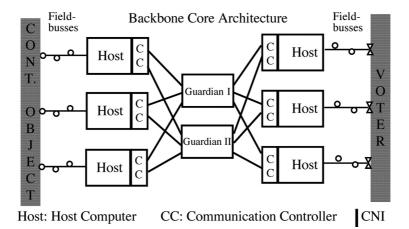

The keynote presentation for the session on Real-Time Control was given by *Hermann Kopetz* (Technical University of Vienna); he stressed the importance of having a fault-hypothesis for safety-critical real-time systems. Kopetz concluded that (a) the design of safety-critical computing systems requires a fault-tolerant architecture and a rigorous design methodology, (b) the precise specification of

the fault hypothesis is the key document in the design of fault-tolerant systems, and (c) the architecture of a safety critical application must tolerate the arbitrary failure of any single VLSI chip since one cannot assume that a chip contains two independent fault containment regions.

The Services and Components session started with the keynote by *K. Venkatesh Prasad* (Leader Ford Motor Company's Infotronics Technologies Group). He sketched the future of automotive product creation, involving the rapid convergence of enterprise and embedded computing and of portable-mobile, fixed-mobile and fixed wireless communications. Prasad argued that creating an automobile clearly calls for a series of innovations that in turn rely on a body of inventions, literature and competencies that are created and nurtured in academia and the broad industrial and public sector research & development base. This highlighted the emerging role of software technologies and processes in modern automotive product creation, and stimulated thinking in terms of how academic curricula might need to evolve and what types of new collaboration styles might be needed for the creation of sustainable mobility solutions in the future.

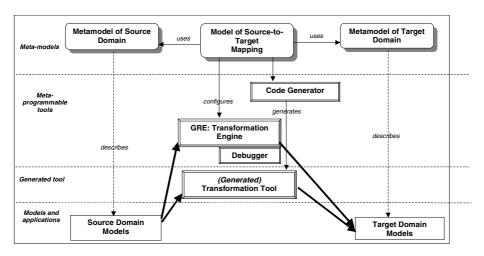

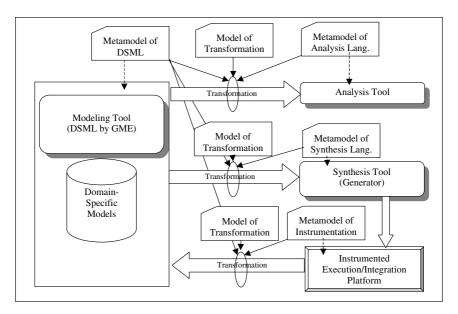

Janos Sztipanovits (Vanderbilt University) delivered the keynote speech, titled "Model-Integrated Computing", for the session on Model-Based Development, and Tools. Sztipanovits pointed out that despite it being a seemingly simple concept, building large systems from components is a very hard problem. In particular, the side-effects of component composition as manifested in component interactions often transpire only during system integration (compositionality problem), and the responsibility for design integrity lies with each system integrator (semantics problem). These problems are aggravated by physical requirements that cross-cut functional component-boundaries, and thus defy compositionality. Sztipanovits identified the following challenges for model-integrated computing: the creation and application of domain specific modeling languages (DSMLs), model synthesis, and model transformation. He then promoted the use of meta-modeling as a means for capturing the semantics of different target languages and execution models; he distinguished between domain models as capturing designs, and meta-models as capturing design invariants (such as types, constraints, and well-formedness rules). Sztipanovits also discussed the Generic Modeling Environment (GME), developed at Vanderbilt University, based on meta-modeling and model-transformation concepts. He concluded that domainspecific modeling languages and model-transformations are key technologies for future progress in embedded systems development, and that model-integrated computing is becoming a mature technology for the development of complex applications.

Two panel discussions complemented the keynote presentations. The first panel discussed "Research Challenges in Automotive Software" as well as the role of academia, industry and funding agencies in addressing these challenges. Panelists were *Hans-Georg Frischkorn* (then BMW Group), *K. Venkatesh Prasad* (Ford Motor Company), *Dev Kambhampati* (UC Discovery) and *Ramesh Rao* (California Institute for Telecommunications and Information Technology). Dis-

cussions emphasized the importance of software architectures in automotive software development and research, their integration into effective development processes, the availability of a defined middleware platform, the view of automotive software within broader system boundaries and the importance of user experience in the automotive design. The discussion also highlighted the need for an increased understanding of software as a product on the sides of both manufacturers and suppliers, the availability of business plans taking software into account, and access to engineers trained in system architecture and integration. Collaboration between industry and academia, as well as long-term fundamental research, is required to address these issues.

The second panel discussed "Challenges in Model-Based Design of Automotive Software". Panelists were Werner Damm (University of Oldenburg, Germany), Edward C. Nelson (Ford Motor Company), Jürgen Bielefeld (BMW Group) and Carlo Ghezzi (Politecnico di Milano, Italy). The discussion emphasized the importance of models that need to be kept consistent with software implementations and allow for incremental development and variant/product-line management. Models were also identified as a good means of communication between manufacturer and supplier. The importance of capturing system-wide views, such as the interactions of different system components, was also highlighted in the discussion. The utility of partial views, focused on separate services and addressing multiple levels of abstraction, was identified. Further research in developing modeling languages with thoroughly worked-out theories addressing the semantic level was suggested; a model repository was proposed as a valuable tool for the research community to compare modeling approaches and tools.

#### Selected Papers

This volume includes a selection of refereed technical and invited papers presented at the workshop. In the following we give a brief overview of the selected papers and their contents.

The contribution "Analyzing the Worst-Case Execution Time by Abstract Interpretation of Executable Code" by *Christian Ferdinand et al.*, addresses the validation of timing behaviors and memory usage as it occurs in embedded microprocessors by means of abstract interpretation of executable code.

In their paper "Quality Assurance and Certification of Software Modules in Safety Critical Automotive Electronic Control Units Using a CASE-Tool Integration Platform", Klaus Müller-Glaser et al. describe a CASE tool integration platform for quality assurance and certification of software modules.

In "On the Fault Hypothesis for a Safety-Critical Real-Time System", the paper accompanying his keynote presentation, *Hermann Kopetz* discusses the critical role of systematic failure management for systems prevelant in the automotive domain. This includes, in particular, the formulation of an explicit fault hypothesis, which has important consequences especially for the architecture design of safety-critical systems.

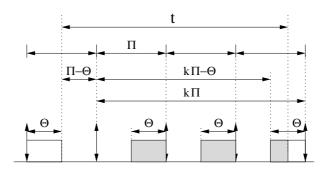

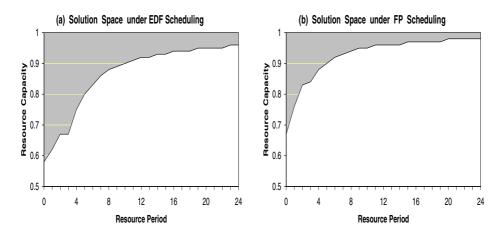

In "A Compositional Framework for Real-Time Guarantees", *Insup Lee et al.* describe a formal approach for establishing real-time properties for a composite system out of real-time properties for its parts.

Carlo Ghezzi et al. propose modeling component and service federations in "Validation of Component and Service Federations in Automotive Software Applications". Component federations can be modeled using statecharts (for individual components) and MSC variants (for interaction properties); service federations can be described using static architectural models, constraints on model transformations, and sequence diagrams for interaction properties.

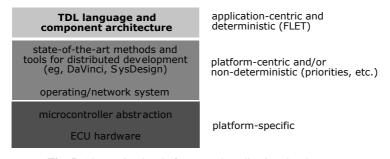

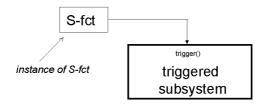

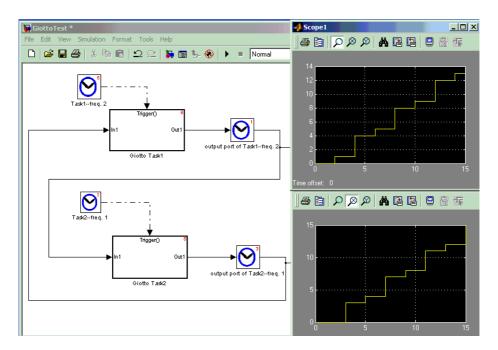

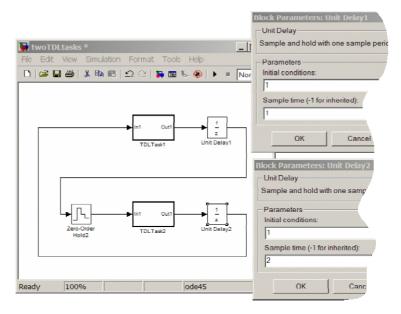

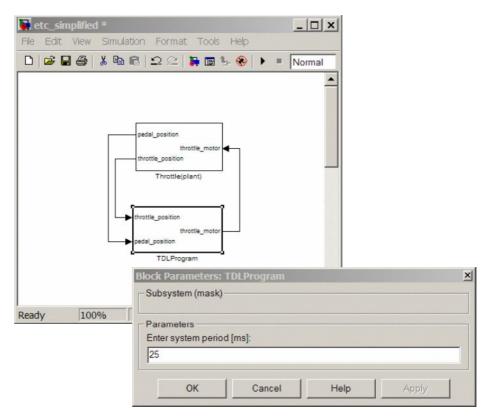

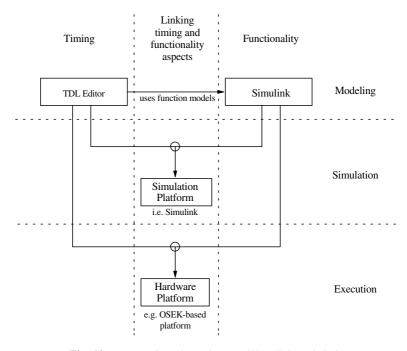

The paper "Towards a Component Architecture for Hard Real Time Control Applications" by Wolfgang Pree and Josef Templ describes Giotto, a platform-independent, deterministic software model for embedded systems, with the goal of abstracting from the target hardware platform in the early development stages, and of supporting moving code modules from one ECU to another in the target system. One challenge addressed by Giotto is to specify timing-behavior independently from concrete scheduling algorithms and communication platforms.

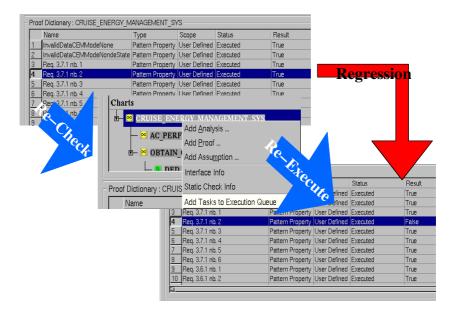

In "Adding Value to Automotive Models", Werner Damm et al. describe advanced code-generation and validation techniques as a means for adding value to the models themselves. This can be accomplished by means of in-depth knowledge of the formal semantics behind the corresponding modeling tools, in-depth knowledge of the use of these tools, and extensive cooperation with the corresponding tool vendors.

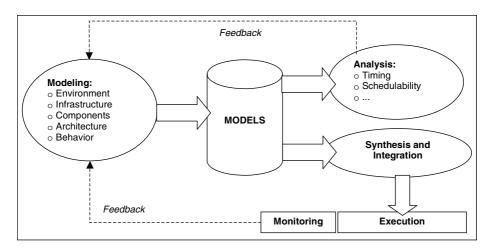

Gabor Karsai, in "Automotive Software: A Challenge and Opportunity for Model-Based Software Development", identifies modeling and model-transformation as a common theme across the model-construction, analysis, and synthesis and integration phases of system development. According to Karsai, this makes the case for meta-programmable tools and corresponding tool-chains.

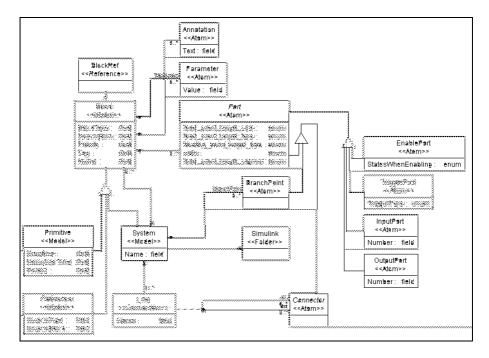

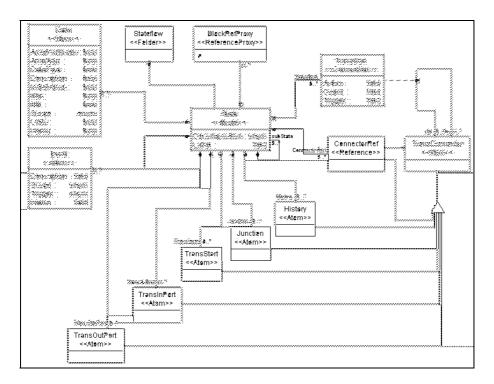

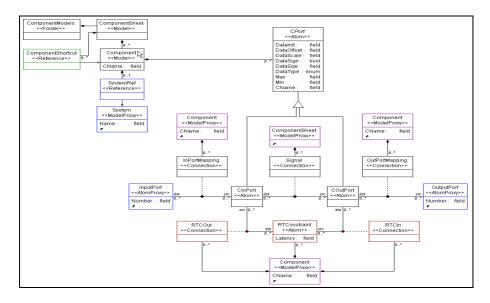

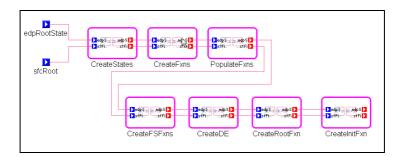

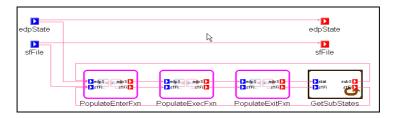

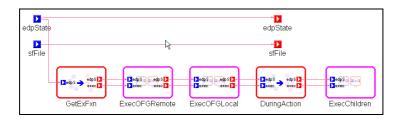

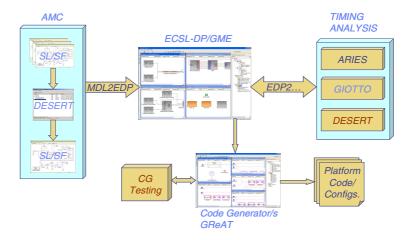

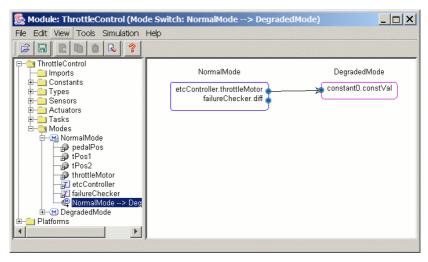

The paper "Software for Automotive Systems: Model-Integrated Computing" by *Sandeep Neema et al.* presents an exemplary design flow for automotive system development based on the Generic Modeling Environment (GME) and tool connectors for Simulink/Stateflow, Matlab, and specific code generators for the target platform.

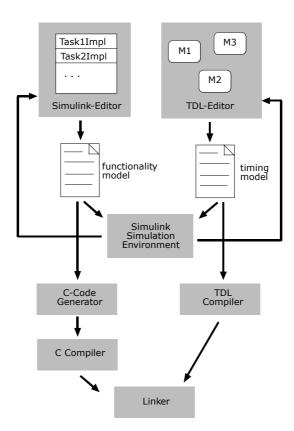

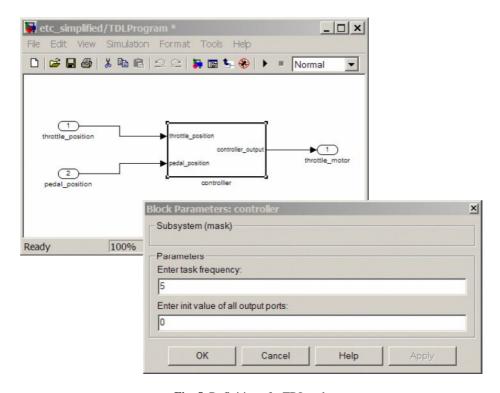

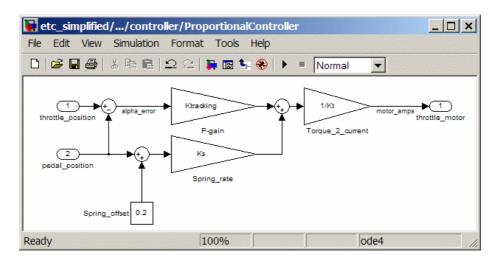

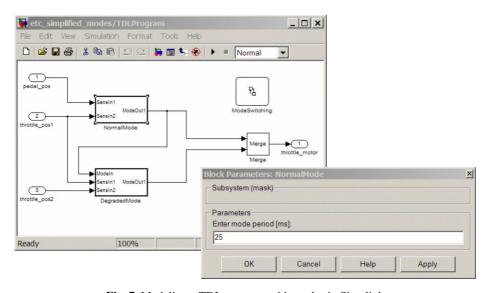

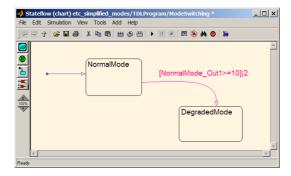

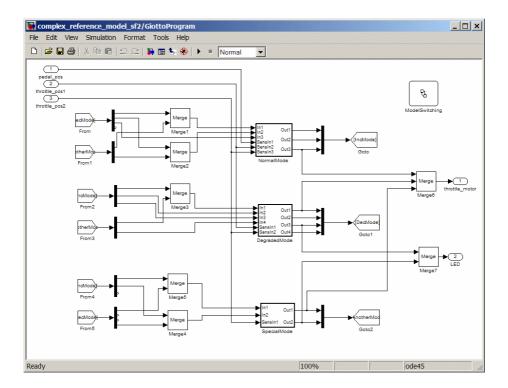

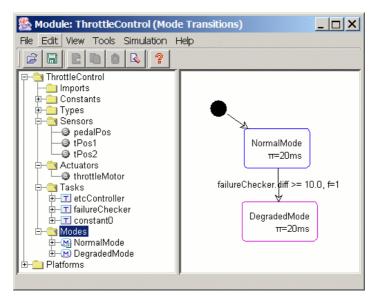

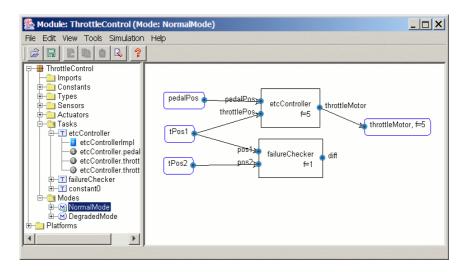

Finally, in "Simulink Integration of Giotto/TDL", Wolfgang Pree et al. report on a case study carried out together with BMW on a throttle control; in this case study, the executable code was generated fully automatically from specifications of both the timing and the functional model. Using specialized translators the properties as specified in Simulink were transformed and simulated within a dedicated tool-set.

#### Outcome

The workshop clearly exhibited the state-of-the-art of automotive software engineering and pointed out various challenges in the area. This is also reflected by the papers selected for this volume. In particular, the idea of the workshop to bring together leading engineers from the Automotive domain with key researchers on an international level also stimulating the discussion between Europe and the US proved to be very fruitful and worked out perfectly. During the workshop significant progress was achieved towards developing a common understanding of the challenging problems in the automotive domain such as:

#### X Preface

- standards for architectures and ways of structuring software systems in cars,

- a careful collection of significant data about the reliability of software in cars today and methodological steps to improve the reliability,

- better ways to model cars with respect to their software properties and structures during the development process,

- more sophisticated development processes incorporating recent scientific results from academia to improve the quality checking.

At the end of the workshop and also thereafter participants strongly expressed their satisfaction about the workshop and its usefulness to stimulate further research and progress in the area of automotive software engineering. Altogether the workshop was an overall success proving that the concept of the workshop accurately addressed the relevant issues and the appropriate community.

The organizers and editors extend their profound thanks to all workshop participants, authors, keynote speakers, panelists, reviewers, sponsors and members of the local organization team for their important contributions to the success of the workshop itself and of this post-proceedings volume.

March 2006

Manfred Broy Ingolf H. Krüger Michael Meisinger

# **Organizers**

Manfred Broy Ingolf H. Krüger

#### Referees

Scott Andrews

Luciano Baresi

Frederic Doucet

Carlo Ghezzi

Rajesh Gupta

Gabor Karsai

Luciano Lavagno

Insup Lee

Michael Meisinger

Massimiliano Menarini

Klaus D. Müller-Glaser

Edward C. Nelson

Wolfgang Pree

Insik Shin

Janos Sztipanovits

# Local Arrangements

David Bareno Martha Chavez Diwaker Gupta Ingolf H. Krüger Jennifer Lee Russell McClure Don Peters-Coville Sabine Rittmann Marilyn Samms

#### XII Organization

# **Sponsors**

California Institute for Telecommunication and Information Technology (Calit2) National Science Foundation (NSF) ARTIST, European Union (EU) Deutsche Forschungsgemeinschaft (DFG)

Deutsche Forschungsgemeinschaft

**DFG**

# **Table of Contents**

# Quality Assurance

| Analyzing the Worst-Case Execution Time by Abstract Interpretation of Executable Code                                                                       |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Christian Ferdinand, Reinhold Heckmann, Reinhard Wilhelm                                                                                                    | 1   |

| Quality Assurance and Certification of Software Modules in Safety<br>Critical Automotive Electronic Control Units Using a CASE-Tool<br>Integration Platform |     |

| Klaus D. Mueller-Glaser, Clemens Reichmann, Markus Kuehl,<br>Stefan Benz                                                                                    | 15  |

| Real-Time Control                                                                                                                                           |     |

| On the Fault Hypothesis for a Safety-Critical Real-Time System  Hermann Kopetz                                                                              | 31  |

| A Compositional Framework for Real-Time Guarantees  Insik Shin, Insup Lee                                                                                   | 43  |

| Services and Components                                                                                                                                     |     |

| Validation of Component and Service Federations in Automotive<br>Software Applications<br>Luciano Baresi, Carlo Ghezzi                                      | 57  |

| Towards a Component Architecture for Hard Real Time Control<br>Applications                                                                                 |     |

| Wolfgang Pree, Josef Templ                                                                                                                                  | 74  |

| Model-Based Development and Tools                                                                                                                           |     |

| Adding Value to Automotive Models  Eckard Böde, Werner Damm, Jarl Høyem, Bernhard Josko,  Jürgen Niehaus, Marc Segelken                                     | 86  |

| Automotive Software: A Challenge and Opportunity for Model-Based Software Development                                                                       | 40- |

| Gabor Karsai                                                                                                                                                | 103 |

# XIV Table of Contents

| Software for Automotive Systems: Model-Integrated Computing Sandeep Neema, Gabor Karsai | 116 |

|-----------------------------------------------------------------------------------------|-----|

| Simulink Integration of Giotto/TDL  Wolfgang Pree, Gerald Stieglbauer, Josef Templ      | 137 |

| Author Index                                                                            | 155 |

# Analyzing the Worst-Case Execution Time by Abstract Interpretation of Executable Code

Christian Ferdinand<sup>1</sup>, Reinhold Heckmann<sup>1</sup>, and Reinhard Wilhelm<sup>2</sup>

<sup>1</sup> AbsInt Angewandte Informatik GmbH Science Park 1, D-66123 Saarbrücken, Germany info@absint.com http://www.absint.com

<sup>2</sup> Universität des Saarlandes, Postfach 15 11 50, D-66041 Saarbrücken, Germany wilhelm@cs.uni-sb.de http://rw4.cs.uni-sb.de

**Abstract.** Determining the worst-case execution times (WCETs) of tasks in safety-critical hard real-time systems is a difficult problem. A combination of automatic analysis techniques with a few user annotations yields precise WCET estimates.

#### 1 Introduction

Many tasks in safety-critical embedded systems have hard real-time characteristics. Failure to meet deadlines may result in the loss of life or in large damages. Utmost carefulness and state-of-the-art machinery have to be applied to make sure that all requirements are met. To do so lies in the responsibility of the system designer(s).

The problem of finding estimates (precise upper bounds) for the worst-case execution times (WCETs) of tasks in embedded applications is difficult for various reasons [1]. There is typically a large gap between the cycle times of modern microprocessors and the access times of main memory. Caches and branch target buffers are used to overcome this gap in virtually all performance-oriented processors (including high-performance microcontrollers and DSPs). Pipelines enable acceleration by overlapping the executions of different instructions. The consequence is that the execution behavior of the instructions cannot be analyzed separately since it depends on the execution history.

Cache memories usually work very well, but under some circumstances minimal changes in the program code or program input may lead to dramatic changes in cache behavior. For (hard) real-time systems, this is undesirable and possibly even hazardous. The widely used classical methods of predicting execution times are not generally applicable. Software monitoring or the dual-loop benchmark change the code, what in turn has impact on the cache behavior. Hardware simulation, emulation, or direct measurement with logic analyzers can only determine the execution time for one input. This cannot be used to infer the execution times for all possible inputs in general. Making the safe—yet for the most part—unrealistic assumption that all memory references lead to cache misses results in the execution time being overestimated by several hundred percent.

Abstract interpretation can be used to efficiently compute a safe approximation for all possible cache and pipeline states that can occur at a program point. These results can be combined with ILP (Integer Linear Programming) techniques to safely predict the worst-case execution time and a corresponding worst-case execution path.

Apart from the executable program to be analyzed, the analyzers rely on user input to find a result at all, or to improve the precision of the result. The most important user annotations specify the targets of computed calls and branches and the maximum iteration counts of loops. We also present automatic analyses to determine the targets of computed branches and calls automatically in typical cases for code compiled from C and an automatic loop bound analysis for loops with constant bounds. Furthermore, we show how these analyses can be extended to handle code produced with the help of typical code generator tools widely used in the automotive area.

Sect. 2 introduces **AbsInt**'s **aiT** tool for WCET analysis. Sect. 3 describes the working of **aiT**, i.e. the various analysis algorithms. Sect. 4 presents various possibilities for user annotations that help **aiT** in doing its work. Sect. 5 deals with a side issue, namely stack analysis. Future work is discussed in Sect. 6, and Sect. 7 concludes.

# 2 aiT – WCET Analyzers

The **AbsInt** company has created a family of WCET analyzer tools called **aiT**. The **aiT** tools get as input an executable, user annotations as described in Sect. 4, a description of the (external) memories and buses (i.e. a list of memory areas with minimal and maximal access times), and a task (identified by a start address). A task denotes a sequentially executed piece of code (no threads, no parallelism, and no waiting for external events). This should not be confused with a task in an operating system that might include code for synchronization or communication.

The WCET analyzers compute an upper bound of the runtime of the task (assuming no interference from the outside). Effects of interrupts, IO and timer (co-)processors are not reflected in the predicted runtime and have to be considered separately (e.g., by a quantitative analysis).

In addition to the raw information about the WCET, several aspects can be visualized by the aiSee tool [2] to view detailed information delivered by the analysis.

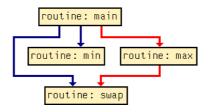

Figure 1 shows the graphical representation of the call graph for some small example as produced by **aiT**. The calls (edges) that contribute to the worst-case runtime are marked by the color red. The computed WCET is given in CPU cycles and in microseconds provided that the cycle time of the processor has been specified.

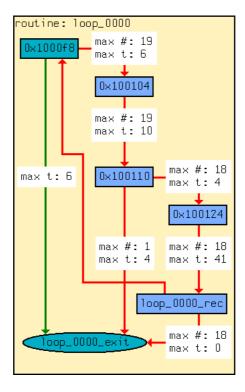

Figure 2 shows the basic block graph of a loop. The number max # describes the maximal number of traversals of an edge in the worst case, while max t describes the maximal execution time of the basic block from which the edge originates

Worst Case Execution Time: 2389 cycles = 53.089 us

Fig. 1. Call graph with WCET results

(taking into account that the basic block is left via the edge). The worst-case path, the iteration numbers and timings are determined automatically by **aiT**.

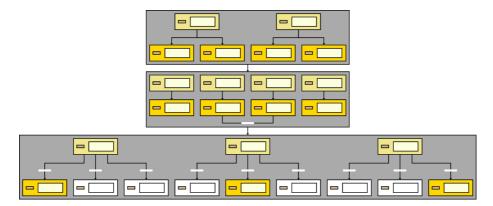

Figure 3 shows the possible pipeline states for a basic block in this example. Such pictures are shown by **aiT** upon special demand. The large dark grey boxes correspond to the instructions of the basic block, and the smaller rectangles in them stand for individual pipeline states. Their cyclewise evolution is indicated by the strokes connecting them. Each layer in the trees corresponds to one CPU cycle. Branches in the trees are caused by conditions that could not be statically evaluated, e.g., a memory access with unknown address in presence of memory areas with different access times. On the other hand, two pipeline states fall together when details they differ in leave the pipeline. This happened for instance at the end of the second instruction, reducing the number of states from four to three

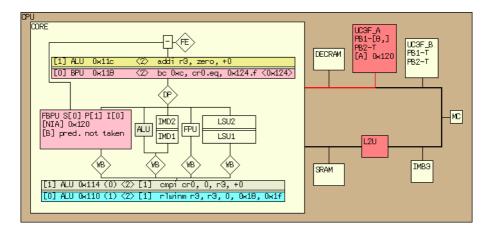

Figure 4 shows part of the top left pipeline state from Fig. 3 in greater magnification. It displays a diagram of the architecture of the CPU (in this case a PowerPC 555) showing the occupancy of the various pipeline stages with the instructions currently being executed.

#### 3 Worst-Case Execution Time Prediction

In this section, we describe the working of **aiT** in greater detail.

#### 3.1 Phases of WCET Computation

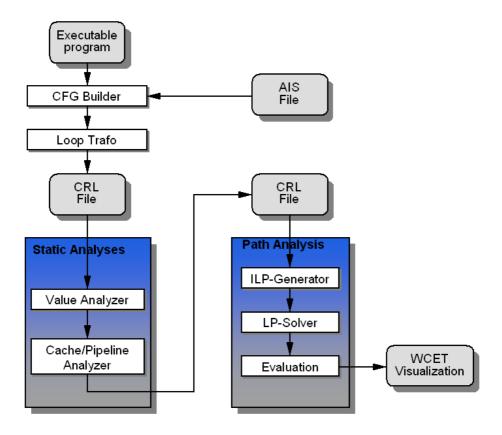

In our approach [3] the determination of the WCET of a program task is composed of several phases (see Fig. 5):

- CFG Building: Decoding, i.e. identification of instructions, and reconstruction of the control-flow graph (CFG) from a binary program;

- Value Analysis: computation of address ranges for instructions accessing memory;

- Cache Analysis: classification of memory references as cache misses or hits [4];

Fig. 2. Basic block graph in a loop, with timing information

- Pipeline Analysis: prediction of the behavior of the program on the processor pipeline [5];

- Path Analysis: determination of a worst-case execution path of the program [6].

The results of value analysis are used by the cache analysis to predict the behavior of the (data) cache. The results of cache analysis are used within pipeline analysis allowing the prediction of pipeline stalls due to cache misses. The combined results of the cache and pipeline analyses are used to compute the execution times of program paths. The separation of WCET determination into several phases has the additional effect that different methods tailored to the subtasks can be used. Value analysis, cache analysis, and pipeline analysis are done by abstract interpretation [7], a semantics-based method for static program analysis. Integer linear programming is used for path analysis. The various phases are presented in more detail in the following subsections.

#### 3.2 Reconstruction of the Control Flow from Binary Programs

The Control-Flow Graph Builder (CFG Builder) has two inputs: the executable program, and a so-called AIS file containing the user annotations. In the first step a decoder reads the program, identifies the instructions and their operands,

Fig. 3. Possible pipeline states in a basic block

and reconstructs the control flow [8,9]. This requires some knowledge about the underlying hardware, e.g., which instructions represent branches or calls. A subsequent *loop transformation* identifies loops and marks them for special treatment (see Sect. 3.7).

The resulting control-flow graph is annotated with the information from the AIS file needed by subsequent analyses and then translated into CRL (Control-Flow Representation Language). This annotated control-flow graph is forwarded to the various analyzers. Each analyzer adds its results to the graph by means of CRL attributes so that they are available in all subsequent analysis steps.

The decoder can find the target addresses of absolute and pc-relative calls and branches, but may have difficulties with target addresses computed from register contents. Thus, aiT uses specialized decoders that are adapted to certain code generators and/or compilers. They usually can recognize branches to a previously stored return address, and know the typical compiler-generated patterns of branches via switch tables. Yet non-trivial applications may still contain some computed calls and branches (in handwritten assembly code) that cannot be resolved by the decoder; these unresolved computed calls and branches are documented by appropriate messages and require user annotations (see Sect. 4). Such annotations may list the possible targets of computed calls and branches, or tell the decoder about the address and format of an array of function pointers or a switch table used in the computed call or branch.

## 3.3 Value Analysis

Value analysis tries to determine the values in the processor registers for every program point and execution context. Often it cannot determine these values exactly, but only finds safe lower and upper bounds, i.e. intervals that are guaranteed to contain the exact values. A subtask of value analysis is loop bound analysis, which tries to find the maximum iteration numbers of loops (see Sect. 3.8). The results of value analysis are also used to determine possible addresses of indirect memory accesses—an information important for cache analysis.

Fig. 4. Individual pipeline state

#### 3.4 Cache Analysis

Cache analysis classifies the accesses to main memory. The analysis in our tool is based upon [4], which handles analysis of caches with LRU (Least Recently Used) replacement strategy. However, it had to be modified to reflect the non-LRU replacement strategies of common microprocessors: the pseudo-round-robin replacement policy of the ColdFire MCF 5307, and the PLRU (Pseudo-LRU) strategy of the PowerPC MPC 750 and 755. The modified algorithms distinguish between sure cache hits and unclassified accesses. The deviation from perfect LRU is the reason for the reduced predictability of the cache contents in case of ColdFire 5307 and PowerPC 750/755 compared to processors with perfect LRU caches [10].

## 3.5 Pipeline Analysis

Pipeline analysis models the pipeline behavior to determine execution times for a sequential flow (basic block) of instructions, as done in [5,11]. It takes into account the current pipeline state(s), in particular resource occupancies, contents of prefetch queues, grouping of instructions, and classification of memory references as cache hits or misses. The result is an execution time for each instruction in each distinguished execution context.

# 3.6 Path Analysis

Using the results of the micro-architecture analyses, path analysis determines a safe estimate of the WCET. The program's control flow is modeled by an integer linear program [6,12] so that the solution to the objective function is the predicted worst-case execution time for the input program. A special mapping of variable names to basic blocks in the integer linear program enables execution and traversal counts for every basic block and edge to be computed.

Fig. 5. Phases of WCET computation

## 3.7 Analysis of Loops and Recursive Procedures

Loops and recursive procedures are of special interest since programs spend most of their runtime there. Treating them naively when analyzing programs for their cache and pipeline behavior results in a high loss of precision.

Frequently the first execution of the loop body loads the cache, and subsequent executions find most of their referenced memory blocks in the cache. Because of speculative prefetching, cache contents may still change considerably during the second iteration. Therefore, the first few iterations of the loop often encounter cache contents quite different from those of later iterations. Hence it is useful to distinguish the first few iterations of loops from the others. This is done in the VIVU approach (virtual inlining, virtual unrolling) [13].

Using upper bounds on the number of loop iterations, the analyses can virtually unroll not only the first few iterations, but all iterations. The analyses can then distinguish more contexts and the precision of the results is increased—at the expense of higher analysis times.

#### 3.8 Loop Bound Analysis

WCET analysis requires that upper bounds for the iteration numbers of all loops be known. **aiT** tries to determine the number of loop iterations by *loop bound analysis*, but succeeds in doing so for simple loops only. Bounds for the iteration numbers of the remaining loops must be provided as user annotations (see Sect. 4).

Loop bound analysis relies on a combination of value analysis (see Sect. 3.3) and pattern matching, which looks for typical loop patterns. In general, these loop patterns depend on the code generator and/or compiler used to generate the code that is being analyzed. There are special **aiT** versions adapted to various generators and compilers.

Normally, loop bounds can only be determined if all relevant data (loop counter etc.) are held in registers. The reason is that data held in memory locations might be altered by accesses to unknown memory addresses. An exception is made for code generated by known code generation tools, e.g.,

```

for((map->ctr1->low=1);(map->ctr1->low<=3);(map->ctr1->low++)){

for((map->ctr2->low=1);(map->ctr2->low<=6);(map->ctr2->low++)){

/* code with memory accesses via pointers ... */

}

}

```

Here, **aiT** assumes that the generated code is well-behaved so that the memory accesses in the loop body do not affect the loop counters. To be on the safe side, **aiT** issues a message about this assumption and asks the user to verify it manually.

Another common type of loops in generated code is linear search in a sorted array, e.g.,

```

while (x > *(x_table++)) \dots

```

Here, there is the risk that  $\mathbf{x}$  is greater than all table values so that the loop continues examining values beyond the end of the table in an uncontrolled way. Yet again,  $\mathbf{aiT}$  assumes that the code generator has avoided this error situation by an extra test before the loop or by putting the largest possible value at the end of the table. Then the number of executions of the loop header is bounded by the size of the table. Again,  $\mathbf{aiT}$  issues a message asking the user to verify that the assumption is valid.

#### 4 User Annotations

Apart from the executable, **aiT** needs user input to find a result at all, or to improve the precision of the result. These user annotations may be supplied in a special file, the so-called AIS file (see Fig. 5), or as special comments in the source code (see Sect. 4.3). The most important user annotations specify the targets of computed calls and branches and the maximum iteration counts of loops (there are many other possible annotations).

#### 4.1 Targets of Computed Calls and Branches

For a correct reconstruction of the control flow from the binary, targets of computed calls and branches must be known.  $\mathbf{aiT}$  can find many of these targets automatically for code compiled from C. This is done by identifying and interpreting switch tables and static arrays of function pointers. Yet dynamic use of function pointers cannot be tracked by  $\mathbf{aiT}$ , and hand-written assembly code in library functions often contains difficult computed branches. Targets for computed calls and branches that are not found by  $\mathbf{aiT}$  must be specified by the user. This can be done by writing specifications of the following forms in a parameter file called AIS file:

```

INSTRUCTION ProgramPoint CALLS Target_1, ..., Target_n; INSTRUCTION ProgramPoint BRANCHES TO Target_1, ..., Target_n;

```

ARM7 TDMI processors do not offer return instructions. Instead, various kinds of computed branches with the return address as target can be employed. aiT can recognize most of these branches as returns. The few remaining ones, mostly contained in library code, can be annotated as follows:

```

INSTRUCTION ProgramPoint IS A RETURN;

```

Program points are not restricted to simple addresses. A program point description particularly suited for CALLS and BRANCHES specifications is "R" + n COMPUTED which refers to the nth computed call or branch in routine R—counted statically in the sense of increasing addresses, not dynamically following the control flow. In a similar way, targets can be specified as absolute addresses, or relative to a routine entry in the form "R" + n BYTES or relative to the address of the conditional branch instruction, which is denoted by PC.

Example 1. The library routine C\_MEMCPY in TI's standard library for the TMS470 consists of hand-written assembly code. It contains 2 computed branches whose targets can be specified as follows:

```

instruction "C_MEMCPY" + 1 computed

branches to pc + 0x04 bytes, pc + 0x14 bytes, pc + 0x24 bytes;

instruction "C_MEMCPY" + 2 computed

branches to pc + 0x10 bytes, pc + 0x20 bytes;

```

The advantage of such relative specifications is that they work no matter what the absolute address of C\_MEMCPY is.

If the application contains an array P of function pointers, then a call P[i](x) may branch to any address contained in P. aiT tries to obtain the list of these addresses automatically: If the array access and the computed call in the executable are part of a small code pattern as it is typically generated by the compiler, aiT notices that the computed call is performed via this array. If furthermore the array contents are defined in a data segment so that they are statically available, and the array is situated in a ROM area so that its contents cannot be modified,

then **aiT** automatically considers the addresses in the array as possible targets of the computed call.

If array access and computed call are too far apart or realized in an untypical way, **aiT** cannot recognize that they belong together. Similar remarks apply to computed branches via switch tables. In both cases, the array or table belonging to the computed call or branch can be declared in the AIS file. The declaration starts like the ones described above:

```

INSTRUCTION ProgramPoint CALLS VIA ArrayDescriptor;

INSTRUCTION ProgramPoint BRANCHES VIA ArrayDescriptor;

```

Here, the *ArrayDescriptor* describes the address and the format of the table that contains the call or branch targets. These targets are extracted from the table according to the given format rules.

#### 4.2 Loop Bounds

WCET analysis requires that upper bounds for the iteration numbers of all loops be known.  $\mathbf{aiT}$  tries to determine the number of loop iterations by loop bound analysis, but succeeds in doing so only for loops with constant bounds whose code matches certain patterns typically generated by the supported compilers. Bounds for the iteration numbers of the remaining loops must be provided by user annotations. A maximum iteration number of j is specified in the AIS parameter file as follows:

```

LOOP ProgramPoint Qualifier MAX j;

```

A *ProgramPoint* is either an address or an expression of the form "R" + n LOOPS which means the nth loop in routine R counted from 1. *Qualifier* is an optional information:

- begin indicates that the loop test is at the beginning of the loop, as for C's while-loops.

- end indicates that the loop test is at the end of the loop, as for C's dowhile-loops.

If the qualifier is omitted, **aiT** assumes the worst case of the two possibilities, which is **begin** where the loop test is executed one more time. The **begin/end** information refers to the *executable*, not to the source code; the compiler may move the loop test from the beginning to the end, or vice versa.

```

Example 2. loop "_prime" + 1 loop end max 10; specifies that the first loop in _prime has the loop test at the end and is executed at most 10 times.

```

#### 4.3 Source Code Annotations

Specifications can also be included in C source code files as special comments marked by the key string ai:

```

/* ai: specification_1; ... specification_n; */

```

The names of the source files are extracted from the debug information in the executable.

Source code annotations admit a special program point or target here, which roughly denotes the place where the annotation occurs (due to compiler optimizations the debug information is not always precise). More exactly, aiT extracts the correspondence between source lines and code addresses from the executable. A here occurring in source line n then points to the first instruction associated with a line number  $\geq n$ .

For loop annotations, it is not required that here exactly denotes the loop start address. It suffices that it resolves to an address anywhere in the loop as in the following example:

```

for (i=3; i*i <= n; i += 2) {

/* ai: loop here end max 10; */

... }</pre>

```

#### 4.4 Other Annotations

Apart from branch targets and loop bounds, many other properties can be declared in parameter or source files.

- To get any WCET results at all, you must specify upper bounds for the recursion depths of all recursive routines. These specifications are similar to the loop bound specifications described above.

- Flow constraints are linear constraints for the execution counts of basic blocks. For instance,

```

flow (0x100) \le 4 * (0x200);

```

means that the number of executions of the block starting at address 0x100 is at most 4 times the number of executions of the block starting at 0x200. As always, relative addresses or semantic program point descriptions may be used instead of these absolute addresses.

- aiT can be informed about the clock rate of the microprocessor. Knowing the clock rate, aiT can display its results in real time units such as milliseconds.

Without this information, all results are displayed in processor cycles.

- End specifications instruct aiT to stop reading the executable at a certain program point. A possible application is for instance to inform aiT that an interrupt routine called by a software interrupt does not return.

- Value analysis tries to determine register values and addresses of memory accesses. In cases it fails, information about exact addresses or address ranges may be supplied by annotations.

- You may specify that a memory area is read-only or write-only, contains data or code. You may also specify which data it contains.

- You may exclude certain routines from WCET analysis and supply their WCET directly.

- You may specify that a routine never returns (like exit).

- You may specify that a certain basic block is never executed.

- You may specify that a certain condition is always true or always false.

- Program points can be given symbolic names for later reference.

# 5 Stack Analysis

Apart from the timing constraints, embedded applications also face constraints on the memory usage. A possible cause of catastrophic failure is stack overflow that usually leads to run-time errors that are difficult to diagnose. The problem is that the memory area for the stack usually must be reserved by the programmer. Underestimation of the maximum stack usage leads to stack overflow, while overestimation means wasting memory resources. Measuring the maximum stack usage with a debugger is no solution since one only obtains a result for a single program run with fixed input. Even repeated measurements with various inputs cannot guarantee that the maximum stack usage is ever observed. Some, but not all compilers provide information about stack usage, but this requires the availability of the source code, and the information becomes invalid when the generated code is optimized by hand or by some automatic tool.

**AbsInt**'s tool **StackAnalyzer** provides a solution to this problem. It uses the same decoders as **aiT** for reading the executables, and a subset of **aiT**'s annotation language. By concentrating on the value of the stack pointer during value analysis, the tool can figure out how the stack increases and decreases along the various control-flow paths. This information can be used to derive the maximum stack usage of the analyzed task. The predicted worst-case stack usages of the single tasks in a system can be used in an automated overall stack usage analysis for all tasks running on one ECU, as described in [14] for systems managed by an OSEK/VDX real-time operating system.

#### 6 Future Work

Both WCET analysis and stack usage analysis will be extended to cover further microarchitectures. For WCET analysis, the implementation of a pipeline analysis is the major bottleneck in case of modern architectures with features such as super-scalarity, out-of-order execution, branch prediction and folding, and truly parallel execution units. At the moment, an implementation of pipeline analysis is obtained from a pipeline model by a manual coding process. To reduce the realization phase of a pipeline analysis, we are developing a framework to generate these implementations from concise specifications of the models.

The pipeline models themselves need to be specified more formally. With a formal model, analyses on the model itself are possible. With the help of such analyses, the non-determinism in the pipeline analyses can be reduced by limiting the number of successor evolutions that have to be considered for the worst case by identifying one or a few successors that may lead to the global worst case.

The predicted WCETs so far are WCETs of single tasks in one ECU. They can be used to determine an appropriate scheduling scheme for the tasks and to

perform an overall schedulability analysis in order to guarantee that all timing constraints will be met (also called *timing validation*) [15]. **AbsInt** is planning to cooperate with scheduling tool providers to reach this goal in an integrated way. **aiT**'s results can be used in schedulability analysis, and in the opposite direction, information about schedules can help to make **aiT**'s results more precise w.r.t. cache and pipeline states.

#### 7 Conclusion

aiT allows to inspect the timing behavior of (time-critical parts of) program tasks. The analysis results are determined without the need to change the code and hold for all executions (for the intrinsic cache and pipeline behavior). aiT takes into account the combination of all the different hardware characteristics while still obtaining tight upper bounds for the WCET of a given program in reasonable time.

aiT is a WCET tool for industrial usage. Information required for WCET estimation such as computed branch targets and loop bounds is determined by static analysis. For situations where aiT's analysis methods do not succeed, a convenient specification and annotation language was developed in close cooperation with AbsInt's customers. Annotations for library functions (RT, communication) and RTOS functions can be provided in separate files by the respective developers (on source level or separately).

aiT enables development of complex hard real-time systems on state-of-theart hardware, increases safety, and saves development time. Precise timing predictions enable the most cost-efficient hardware to be chosen. As recent trends, e.g., in automotive industries (X-by-wire, time-triggered protocols) require knowledge on the WCETs of tasks, a tool like aiT is of high importance.

#### References

- Wilhelm, R.: Determining bounds on execution times. In Zurawski, R., ed.: Handbook on Embedded Systems. CRC Press (2005) 14-1 - 14-23

- 2. AbsInt Angewandte Informatik GmbH: aiSee Home Page. (http://www.aisee.com)

- Ferdinand, C., Heckmann, R., Langenbach, M., Martin, F., Schmidt, M., Theiling, H., Thesing, S., Wilhelm, R.: Reliable and precise WCET determination for a reallife processor. In: Proceedings of EMSOFT 2001, First Workshop on Embedded Software. Volume 2211 of Lecture Notes in Computer Science., Springer-Verlag (2001) 469–485

- 4. Ferdinand, C.: Cache Behavior Prediction for Real-Time Systems. PhD thesis, Saarland University (1997)

- Langenbach, M., Thesing, S., Heckmann, R.: Pipeline modeling for timing analysis.

In: Proceedings of the 9th International Static Analysis Symposium SAS 2002.

Volume 2477 of Lecture Notes in Computer Science., Springer-Verlag (2002) 294–309

- Theiling, H., Ferdinand, C.: Combining abstract interpretation and ILP for microarchitecture modelling and program path analysis. In: Proceedings of the 19th IEEE Real-Time Systems Symposium, Madrid, Spain (1998) 144–153

- 7. Cousot, P., Cousot, R.: Abstract Interpretation: A Unified Lattice Model for Static Analysis of Programs by Construction or Approximation of Fixpoints. In: Proceedings of the 4th ACM Symposium on Principles of Programming Languages, Los Angeles, California (1977)

- 8. Theiling, H.: Extracting safe and precise control flow from binaries. In: Proceedings of the 7th Conference on Real-Time Computing Systems and Applications, Cheju Island, South Korea (2000)

- Theiling, H.: Generating decision trees for decoding binaries. In: Proceedings of ACM SIGPLAN LCTES/OM 2001, ACM Press (2001) 112–120

- Heckmann, R., Langenbach, M., Thesing, S., Wilhelm, R.: The influence of processor architecture on the design and the results of WCET tools. Proceedings of the IEEE 91 (2003) 1038–1054 Special Issue on Real-Time Systems.

- Schneider, J., Ferdinand, C.: Pipeline behavior prediction for superscalar processors by abstract interpretation. In: Proceedings of ACM SIGPLAN LCTES'99. (1999) 35–44

- Theiling, H.: ILP-based interprocedural path analysis. In Sangiovanni-Vincentelli, A.L., Sifakis, J., eds.: Proceedings of EMSOFT 2002, Second International Conference on Embedded Software. Volume 2491 of Lecture Notes in Computer Science., Springer-Verlag (2002) 349–363

- Martin, F., Alt, M., Wilhelm, R., Ferdinand, C.: Analysis of Loops. In Koskimies, K., ed.: Proceedings of the International Conference on Compiler Construction (CC'98). Volume 1383 of Lecture Notes in Computer Science., Springer-Verlag (1998) 80–94

- Janz, W.: Das OSEK Echtzeitbetriebssystem, Stackverwaltung und statische Stackbedarfsanalyse. In: Embedded World, Nuremberg, Germany (2003)

- Stankovic, J.A.: Real-Time and Embedded Systems. ACM 50th Anniversary Report on Real-Time Computing Research. (1996) http://www-ccs.cs.umass.edu/ sdcr/rt.ps.

# Quality Assurance and Certification of Software Modules in Safety Critical Automotive Electronic Control Units Using a CASE-Tool Integration Platform

Klaus D. Mueller-Glaser<sup>1</sup>, Clemens Reichmann<sup>1</sup>, Markus Kuehl<sup>2</sup>, and Stefan Benz<sup>3</sup>

<sup>1</sup> Institut für Technik der Informationsverarbeitung (ITIV)

Universität Karlsruhe, Engesserstrasse 5, D-76128 Karlsruhe, Germany

{Mueller-Glaser, Reichmann}@itiv.uni-karlsruhe.de

<sup>2</sup> Forschungszentrum Informatik (FZI),

Haid-und-Neustrasse 10-14, D-76128 Karlsruhe, Germany

kuehl@fzi.de

<sup>3</sup> Robert Bosch GmbH, P.O. Box 10 60 50, D-70049 Stuttgart, Germany

Stefan.Benz@de.bosch.com

Abstract. Up to 70 electronic control units (ECU's) serve for safety and comfort functions in a car. Communicating over different bus systems most ECU's perform close loop control functions and reactive functions and have to fulfill hard real time constraints. Some ECU's controlling on board entertainment/office systems are software intensive, incorporating millions of lines of code. The challenge for the design of those distributed and networked control units is to define all requirements and constraints, understand and analyze those manifold interactions between the control units, the car and the environment (driver, road, weather) in normal as well as stress situations (crash). To improve the design of safety critical ECU's we propose an enhanced development process (double-V-model). The use of different modeling descriptions for closed loop control, reactive systems and software intensive systems requires a CASE-tool integration platform. We have developed "GeneralStore" as a platform to support model driven design with heterogeneous models in a design process which is concurrent and distributed between the automotive manufacturer and several suppliers.

#### 1 Introduction

More than 70 electronic control units (ECU's) serve for safety and comfort functions in a luxury car. Communicating over different bus systems (e.g. CAN class C and B [8], LIN [25], MOST [27], Bluetooth [3], [6]). Many ECU's are dealing with close loop control functions as well as reactive functions, they are interfacing to sensors and actuators and have to fulfill safety critical hard real time constraints (thus the software is running under a real time operating and network management system like OSEK/VDX [31] on a standard hardware platform). Other ECU's controlling the onboard infotainment system (video- and audio-entertainment, office-in-the-car with according internet and voice communication, navigation) are really software intensive, incorporating millions of lines of code. All ECU's are connected to the

different buses which in turn are connected through a central gateway to enable the communication among all ECU's.

As new functions in future cars require communication to traffic guidance systems, road condition information systems as well as car to car communication, the software intensive infotainment ECU's will be directly coupled to power train and body control ECU's, even forming closed loop control. Thus, the design of these future systems need to combine methodologies and computer aided design tools for reactive systems and closed loop control systems as well as software intensive systems.

The challenge for the design of those distributed and networked control units is to find and define all requirements and constraints, to understand and analyze those manifold interactions between the many control units, the car and the environment (road, weather etc.) in normal as well as in stress situations (crash), to perform failure mode and effects analysis and to ensure fail safe and fail operational units for safety critical functions. The development process, which is concurrent and distributed between the automotive manufacturer and several suppliers, requires a well understood life-cycle model and a strictly controlled design methodology and using computer aided engineering and design tools to its largest extent.

Design methodologies used today in the automotive industry are focused on the design of distributed functions. Currently, safety and reliability issues are not taken into account from the very beginning of the development process. In the automotive industry the V-model [40] is a well recognized and widely used life cycle model. To include safety and reliability issues from the very beginning we propose in chapter 2 to extend the V-model into a double-V-model where the existing first V describes the development of functions complemented by and interrelated to the second V which handles safety and reliability issues. A well defined information exchange between the activities and products of the two Vs take care of the system safety assessment process, fault tree analysis and failure mode and effects analysis. The methodology is based on certification considerations of complex aircraft systems (SAE ARP 4754 standard [18] and IEC 61508 standard [17]) tailored for automotive applications.

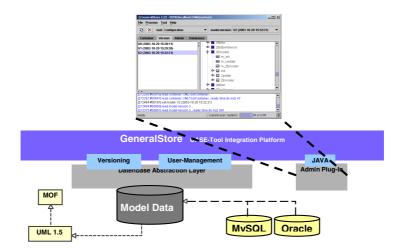

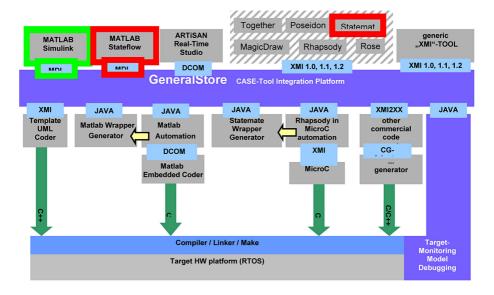

Handling safety issues earlier in the design cycle is just one of the major challenges in automotive electronics. Due to the different description methods preferred for the development of closed loop control functions (power train control), reactive functions (body functions) and software intensive functions (car-infotainment) support is needed to handle heterogeneous models in a model based design methodology. For that purpose we have developed the CASE tool integration platform "GeneralStore". As described in chapter 3 GeneralStore is a MOF, XMI based repository to couple heterogeneous models developed with tools like Matlab/Simulink/Stateflow, Statemate, UML based tools and generic XMI tools. GeneralStore uses commercial code generators as well as a proprietary code generator for handling structural and behavioral descriptions in UML. GeneralStore is developed using Java and the MySQL or Oracle database system. GeneralStore offers functions for check-in/checkout, automatic wrapping, code generation, compile and link as well as versioning and configuration of software modules. Using the double-V development model and GeneralStore we will enhance the development process for safety critical applications and provide more efficiency in model based design.

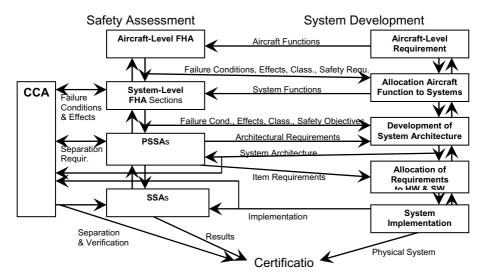

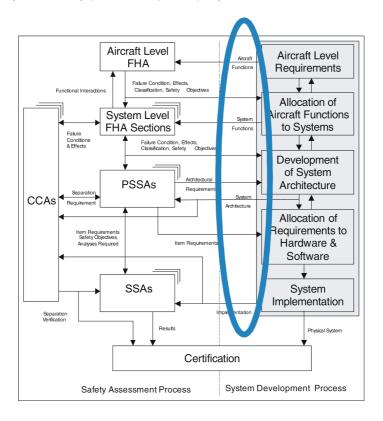

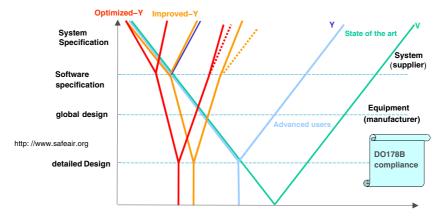

# 2 A Design Methodology for Safety Relevant ECU's

The standard process for the development of automotive electronic systems is based on the "V Model '97", a life cycle process model that is the development standard for embedded electronic systems of the Federal Republic of Germany [40]. Originally intended for information and communication systems it was adapted for other domains, including the automotive domain. However the sequences of design and verification steps is neither standardized nor formalized throughout the automotive domain. Almost every OEM and supplier uses a slightly different design method. In the automotive industry currently large efforts are made to enhance the development of safety critical electronic systems. The aerospace industry (a domain with very standardized and formal development processes) has a lot more experience with safety-critical systems. Aerospace development processes have both function and safety of an aerospace system as the center of focus [24] (Fig.1).

However, the aerospace processes cannot be used directly in the automotive domain, as the boundary conditions and the requirements for safety and reliability in these two domains are different. For example hazard analysis for an airplane explicitly distinguishes between different flight phases (start, cruise, landing). The according phases for cars (start, accelerate, cruise, braking) generally don't make sense. For cars different driving situations are more relevant e.g. for a steer-by-wire system: driving straight ahead, driving curve, pass maneuver, reversing etc., in principle distinguish whether or not the steering wheel needs to be turned or not. Also road conditions should be considered (rain, aquaplaning, ice, off road, gravel, sand, road hole, flange groove).

Besides different analysis processes the most important differentiation is the very low production volume of electronic control units in an airplane in comparison to automotive electronic systems (several thousands vs. several millions), therefore, cost for more hardware components in an airplane preponderate much less than laborintensive and protracted development and test of a new concept. Safety and reliability requirements in airplanes allow for expensive redundancy concepts. Redundancy is necessary in both domains, however, the triple-triple modular hardware redundancy for the primary flight control in a large passenger plane, e.g. the Boeing 777, is by far too expensive in automotive applications, so, double hardware redundancy is common in cars.

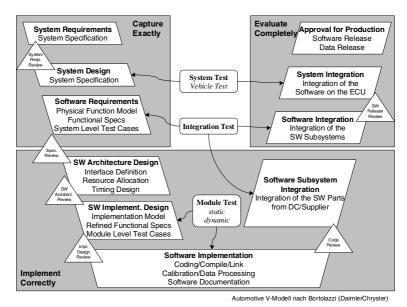

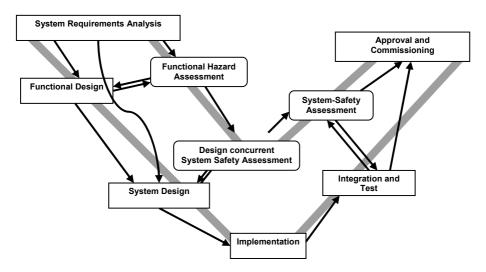

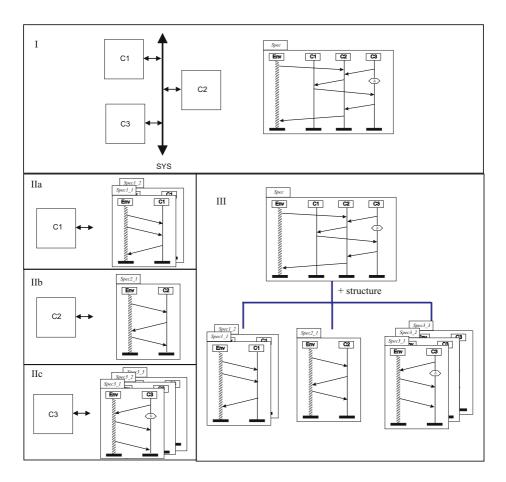

A basic property of system development in aerospace domain is the certification of both, the design process and the designed system (usually by a third party like the Federal Aviation Association FAA). We propose a similar approach to an adapted methodology for the automotive domain which considers safety equally with function and can be described as "double V model". It is based on the V-model [40] (Fig.2 shows the V-model with focus on software development), however, a second V with elements that have a special focus on safety and reliability is added to the original V and connected to it at several appropriate places in the development process. The concepts underlying the additional elements were taken from the aerospace domain and adapted to automotive conditions. Figure 3 gives an overview on the proposed design methodology.

Fig. 1. SAE ARP 4754 standard: safety assessment in parallel to system development

**Fig. 2.** The automotive V-Model with focus on software [7]

In the functional hazard assessment the functional safety requirements for the system are assessed. For this purpose the potential hazards of system functions are determined and classified and, if possible, reliability requirements are derived. Non functional safety requirements (e.g. costs, maintainability, use of standard platforms, mechanical properties like weight and shape) are not considered in the functional

Fig. 3. Overview proposed design methodology

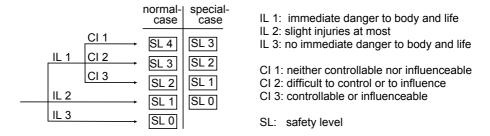

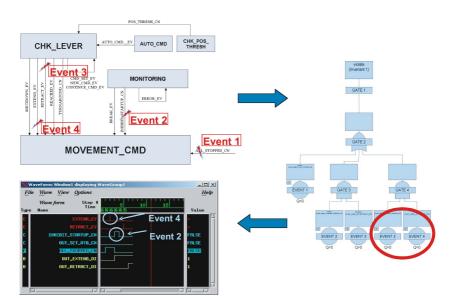

hazard assessment. By a systematic procedure in the early steps of the system development process continuity to subsequent process steps is assured. Based on the system requirements analysis during the functional hazard assessment the system is categorized into risk classes. For this purpose the system is brought in context with its environment, then impacts on the environment and of the environment on the system are analyzed. Like in the concurrent process step functional design the assessment here focuses on the system's functions only. Based on the function list that was generated in the functional design, the corresponding failure conditions are identified and described. For every function there may be several possible failure conditions depending on the system's environmental conditions. The effects of these failure conditions result in possible risks and hazards. These hazards are classified into risk classes based on their severity. This classification is a very critical point in the functional hazard assessment. It should be carried out using a methodology that is adapted to the boundary conditions of the automotive industry (e.g. "CARTRONIC safety analysis" (CSA) according to [5]). Usually a risk graph or decision tree is used; the risk graph of CSA with 5 safety levels ("SL") is shown in figure 4.

Fig. 4. Risk Graph used in CARTRONIC Safety Analysis

The design concurrent system safety assessment is a systematic examination of the system architectures that were proposed during conceptual system design. The goal is a thorough examination whether or not the architecture fulfills the quantitative and qualitative requirements of the functional hazard assessment or if faults or failures can possibly lead to system hazards. The basic idea of the quantitative assessment is the replacement of safety requirements by corresponding reliability requirements in the functional hazard assessment, for example the safety levels SL 1, 2, 3, 4 demand for failure rates less than  $10^{-6}$ /h,  $10^{-7}$ /h,  $10^{-8}$ /h and  $10^{-9}$ /h, respectively [17].

If no quantitative assessment is possible the examination has to take place qualitatively and quantitative results have to be estimated. It is evaluated whether the system architecture and the planned concept design can reasonably be expected to meet the safety requirements and objectives. The methods used are Fault Tree Analysis (FTA) and Markov Analysis (MA) for reliability issues and Failure Mode and Effects Analysis (FMEA) for safety conditions. Common cause errors are examined by common cause analysis (CCA). In addition also other potential hazards than functional hazards are examined. So it is determined whether the system concept design contains additional hazards, esp. hazards that are generated by the system design itself. The method used for this purpose is FMEA. Based on the results of these analyses safety requirements for the design on lower levels (also for hardware and software) and for other systems involved are derived. That way it is ensured that the implementation of the systems fully fulfills its requirements for safety and reliability. Then the design concurrent system safety assessment is repeated for lower system levels. This procedure is supported by several data sources. The most famous database is the MIL-Handbook 217 [9]; though officially discontinued for several years it is still used widely in the civil and military aviation industry. Other databases include the MIL Handbook 978 "NASA Parts Application Handbook", RAC "Non Electronic Parts Reliability Data", RAC "Failure Mode/Mechanism Distribution" and Rome Laboratory's "Reliability Engineer's Toolkit" which provide failure rates for many component types. A major database used in the automotive domain is the "Reliability Data Handbook" of the "Union Technique de l'Electricite" (UTE) [38]. It is to be expected that it will be the successor of the MIL Handbook 217. An example for the application of the UTE handbook can be seen in [38]. In parallel to the process step integration-and-test in system safety assessment the system's conformance to its safety requirements is checked. This is accomplished by the verification of the system's design requirements established in the functional hazard assessment, by a review of the hazard classification of the functional hazard assessment and by verification and validation of other safety requirements. The process of verification and validation as it is known from the V-model takes place in three steps. Here the functional part as well as the non-functional but non-safety part is assessed during integration and test, the issues concerning safety are tested here in the system safety assessment. Generally speaking the procedure in the system safety assessment is very similar to the one during the design concurrent system safety assessment. The same tools are used, but the main difference is now that the system in focus is a physically implemented, real and running system. The same fault tree as in the design concurrent system safety assessment is used again, but the failure rates of the elements in the fault tree no longer come from a database but from the experiences with the real system components. As with system design and design concurrent system safety

assessment the process switches iteratively back and forth between integration and test and system safety assessment. The system is integrated and tested on its correct function, parallel the system's safety properties are proven. For this purpose the system's parts have to fulfill the requirements of the system requirements analysis and especially the quantitative reliability requirements of the functional hazard assessment. The review is done by a systematic examination of the system, its architecture and its realization by various methods of verification and validation (for example testing, fault injection or formal methods). So it is possible to prove that the system fulfills its safety requirements.

As an example for functional hazard assessment two functions of a steer-by-wire system are shown. In turning the steering wheel the driver requests a certain direction in setting an according steering angle. The effective steering moment at the wheels is fed back to the driver by an according steering wheel moment as a haptic feedback. Thus, there are two functions in the function list: 1. steering and 2. feedback steering wheel moment. Analysis identifies the following hazards for function 1: 1.A vehicle does not steer, 1.B steering mechanism blocked, 1.C vehicle steering angle is different from steering wheel set point, and for function 2: 2.A no feedback of steering wheel moment, 2.B steering wheel rotates by itself, 2.C steering wheel blocked. Analysis of

Table 1. Hazard analysis for function steering

| No.   | Function | Hazard                                                                  | Constraint                                  | Effects                                                                                                                    | SL |

|-------|----------|-------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----|

| 1.A.1 | steering | Vehicle does<br>not steer                                               | Steering<br>function<br>currently<br>in use | Death or severe injury of one or<br>more persons possible. Situation is<br>not controllable. Normal case<br>incidence.     | 4  |

| 1.A.2 |          |                                                                         | Steering function currently not in use      | Death or severe injury of one or<br>more persons possible. Situation is<br>not controllable. Special case<br>incidence.    | 3  |

| 1.B.1 |          | Steering<br>mechanism<br>blocked                                        | Steering<br>function<br>currently<br>in use | Death or severe injury of one or<br>more persons possible. Situation is<br>not controllable. Normal case<br>incidence.     | 4  |

| 1.B.2 |          |                                                                         | Steering function currently not in use      | Death or severe injury of one or<br>more persons possible. Situation is<br>not controllable. Special case<br>incidence.    | 3  |

| 1.C.1 |          | Vehicle steering<br>angle different<br>from steering<br>wheel set point | Steering<br>function<br>Currently<br>in use | Death or severe injury of one or<br>more persons possible. Situation is<br>not controllable. Normal case<br>incidence.     | 4  |

| 1.C.2 |          |                                                                         | Steering function currently not in use      | Death or severe injury of one or<br>more persons possible. Situation is<br>difficult to control. Normal case<br>incidence. | 3  |

safety levels results in SL4 for function 1 and SL3 for function 2, as a quantitative reliability requirement the maximum failure rate for steering is 10<sup>-9</sup>/h and 10<sup>-8</sup>/h respectively. Table 1 shows a further refinement of this analysis.

So far we presented the conceptual scheme for a methodology for function-safety-codesign of automotive ECU's. Handling safety issues earlier in the design cycle is just one of the major challenges in automotive electronics. Due to the different description methods actually used in ECU design, support is needed to handle heterogeneous models in a model based design methodology. For that purpose we have developed the CASE tool integration platform "GeneralStore" which will be described in chapter 3.

## 3 GeneralStore - A CASE Tool Integration Platform

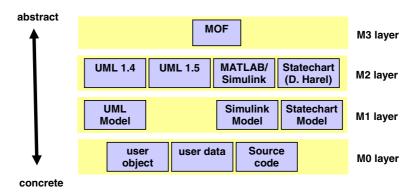

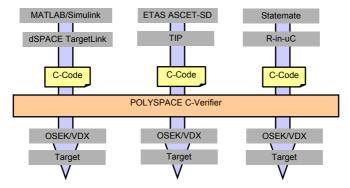

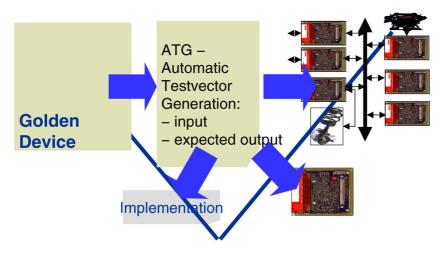

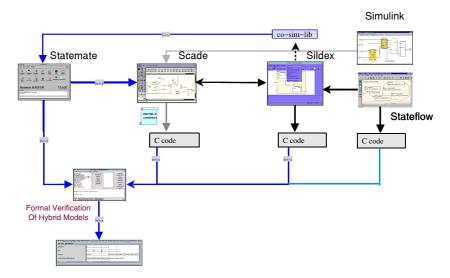

The integration platform GeneralStore is a tool that assists a seamless development process starting with a model and ending with executable code. The software features coupling of subsystems on model level from the above mentioned modeling domains. In addition to object-oriented modeling for software intensive components in embedded systems it supports time-discrete and time-continuous modeling concepts. Our approach provides structural and behavioral modeling with front-end tools and simulation/emulation utilizing back-end tools. Using commercial and proprietary automatic code generators prototype software can be brought into operation on standard hardware platforms rapidly. The Unified Modeling Language (UML) metamodel is used for storing CASE data in a Meta Object Facility (MOF) object repository whereas XMI (XML Metadata Interchange format) is used to interchange this data with UML-CASE-tools. The CASE-tool chain we present in this paper further supports concurrent engineering including versioning and configuration management. It provides adaptors for the tools MATLAB/Simulink/Stateflow and ARTiSAN Real-Time Studio [2], as well as an importer/exporter of UML/XMI. Utilizing the UML notation for an overall system design cycle, the focus of this paper lies on the coupling of heterogeneous subsystems and on a new code generation and coupling approach. While several repository based model-management approaches exist ([1][32][34]) and model driven design is subject to related work ([10][20][21][22][23]) to our knowledge GeneralStore is the only existing platform allowing hetrogeneous concurrent engineering with executable models.

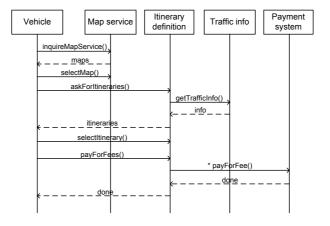

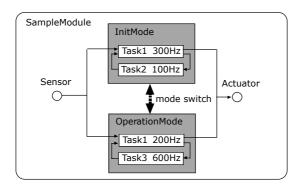

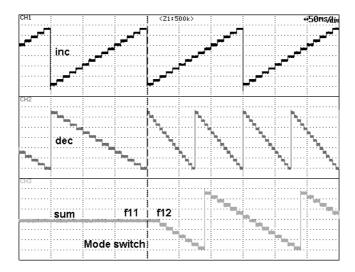

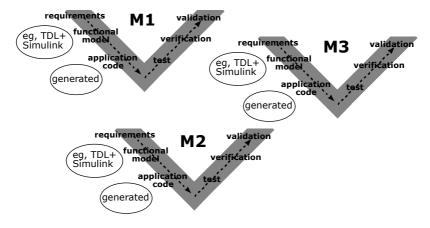

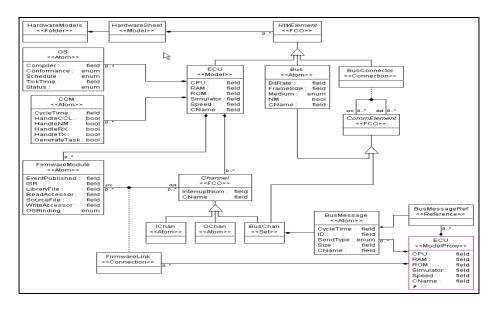

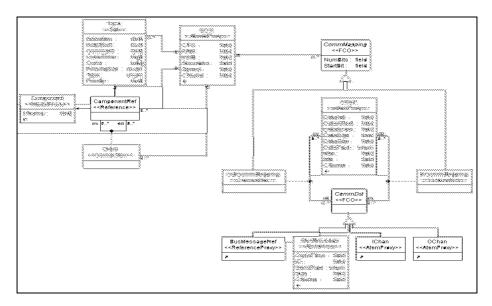

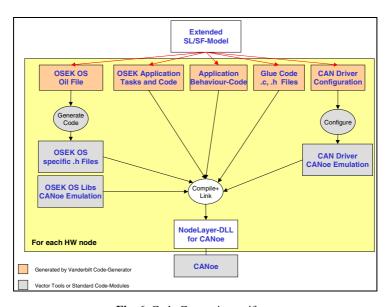

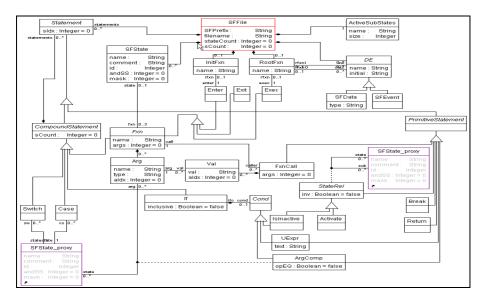

#### 3.1 Metamodeling